Why Firmware-first decisions save months

Firmware is the bridge between hardware and higher-level software — and edge timing, drivers and protocols determine what’s feasible. Solving these early avoids downstream rework, reduces field failures, and prevents costly, late-stage fixes.

80%

downstream defects originate from incorrect driver/protocol assumptions fixed too late

40%

fewer integration defects through HIL automation and reduced debug hours

35%

fewer truck rolls and site visits with OTA and signed builds

From signals to stable devices

Transform raw board signals into predictable device behavior through stable drivers, robust protocol handling, and on-device inference. Validate feasibility early with documented latency, accuracy, and power benchmarks. Establish secure telemetry and OTA pipelines to de-risk the path to pilot deployment.

Healthcare

- Improve patient monitoring with contactless vitals using mmWave radar to capture respiration and heart rate from sub-millimeter chest motion—privacy-preserving and ideal for ICU and senior care.

- Enhance bedside safety with resilient edge TinyML performing on-device anomaly detection for pumps, cabinets, and carts—tolerant to power or network loss, with no PHI leaving the room.

Industrial

- Boost assembly accuracy and compliance with vision-assisted QC rigs that guide operators and capture evidence at line speed.

- Strengthen machine reliability through deterministic I/O control and detailed event logging for cells and production stations.

Life Sciences

- Ensure consistent, traceable lab operations with benchtop instrument control that logs runs, calibrations, and governed releases.

- Validate process changes safely using “twin-of-process” simulations to test cycle times, yields, and failure modes before updating SOPs.

Logistics

- Increase equipment uptime with asset-health pilots that track run-hours, generate alerts and enable remote diagnostics for generators and field assets.

- Improve planning accuracy with traffic and occupancy sensing prototypes that feed real-time metrics into operational dashboards.

Technical Capabilities

Rapid prototyping with eval boards and quick-turn sensors & I/O

Timing-critical firmware with Zephyr or FreeRTOS (only where needed)

On-device ML/CV with TFL-Micro, ONNX Runtime or TensorRT

Protocol bridging from Modbus/OPC UA/CAN/RS-485 to MQTT/HTTPS

Connectivity options including Wi-Fi, Ethernet, LTE Cat-M and NB-IoT with store-and-forward

Determinism at the edge, observability everywhere

Predictable behavior

Ensure devices operate reliably under real workloads with hardened firmware and stable timing, even under load.

Safe, reversible updates

Ship OTA updates confidently during field trials with built-in safety checks and rollback paths.

Faster issue resolution

Detect and diagnose incidents quickly through end-to-end traceability of packets, logs, and device state.

Clean operational handoffs

Enable smooth transitions to internal teams and vendors with clear evidence, visibility, and documented behavior.

Bring-up to safe pilot in six steps

Targets & constraints

Define p95 latency, accuracy, power/thermal budgets, environmental limits, and risks. Establish Prototype Readiness Criteria (PRC), an experiment plan, and decision gates.

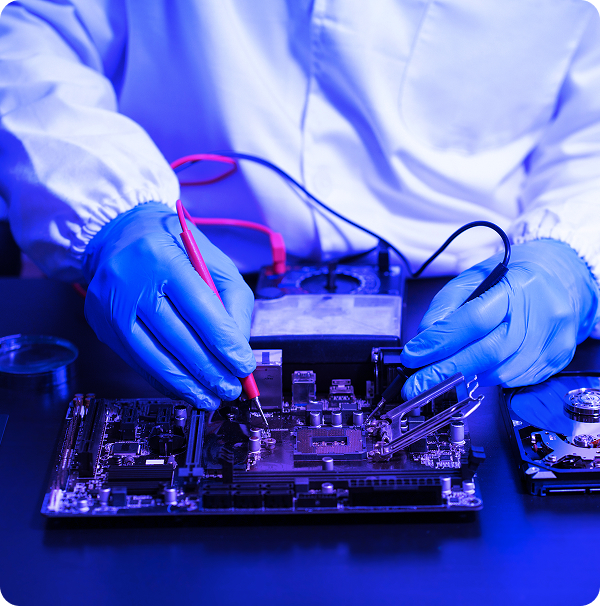

Board bring-up & drivers

Stabilize peripherals and interrupts, validate first data off the board, and create a clean HAL + driver checklist. Produce a “time-to-first-signal” log.

Protocols & edge logic

Implement resilient parsers, retry logic, back-pressure handling, and error codes; add heuristics or on-device ML when useful. Output includes the protocol test matrix, an edge state machine, and failure-mode notes.

Minimal cloud data path

Set up secure ingest, device registry, topics/schemas, alert hooks, and a basic telemetry dashboard. Deliverables include the schema map (device ↔ gateway ↔ cloud), alert rules, and observability hooks.

HIL & Hardening + Security

Build a scriptable test bench for repeatable cross-variant checks; add signed artifacts, OTA updates, and rollback support. Capture automated smoke/regression results, the signed build pipeline, OTA plan, and p95 latency/accuracy table.

Pilot pack & handover

Assemble everything required for a safe pilot: an ops runbook (install → verify → observe), acceptance criteria, ownership map, risk register, and release-notes template.

Outcomes you can audit

Run safer pilots

Ship a pilot-ready build with staged rollouts, rollback paths, and verified update flows.

Make go/no-go decisions faster

Get clarity within 6–10 weeks through defined acceptance criteria and measurable feasibility data.

Accelerate compliance reviews

Provide traceable execution, change history, and a complete audit pack that shortens internal approvals.

Understand real economics

Get a cost-to-serve model for the pilot, support envelope, and realistic scale assumptions.

Scale with confidence

Know what to standardize, productize, outsource, and which next risks should be retired.

Align every stakeholder

Use a concise runbook and ownership map that teams and partners can execute immediately.

Patterns for Code That Reaches the Field

Expert insights to make you future-ready

-

Blog

8 min readHow Agentic AI is Reshaping Last-Mile Logistics in the US E-Commerce Boom

Read MoreThe Last-Mile Delivery Crisis Driving AI Adoption in US E-Commerce

: How Agentic AI is Reshaping Last-Mile Logistics in the US E-Commerce Boom

-

Blog

7 min readWhy Most Zoho Implementations Fail After Year 2?

Read MoreWhy Zoho CRM implementations fail after year 2 and how to fix them.

: Why Most Zoho Implementations Fail After Year 2?

-

Blog

7 min readHow Emerging Technologies Will Redefine Business Models by 2026?

Read MoreHow AI, IoT, and Digital Twins Are Reshaping Business Models

: How Emerging Technologies Will Redefine Business Models by 2026?

-

Blog

7 min readIs Your Zoho Setup Ready to Scale Beyond 50 Users?

Read MoreKey Challenges and Best Practices for Scaling Zoho CRM Beyond 50 Users

: Is Your Zoho Setup Ready to Scale Beyond 50 Users?

-

Blog

4 min readOptimizing Node.js Apps with Modern DevOps Strategy

Read MoreCut Memory Costs and Boost Node.js Performance at Scale

: Optimizing Node.js Apps with Modern DevOps Strategy

-

Blog

7 min readHow to Identify Technology Gaps in Your Business Before Scaling

Read MoreEvaluate IT Infrastructure Before Business Expansion.

: How to Identify Technology Gaps in Your Business Before Scaling

-

Blog

6 min readWhen Should Businesses Hire a Technology Consulting Company

Read MoreKey signs your business needs technology consulting.

: When Should Businesses Hire a Technology Consulting Company

-

Blog

7 min readAgentic AI Frameworks for Autonomous Systems

Read MoreUnderstand how agentic AI enables autonomous decision-driven systems.

: Agentic AI Frameworks for Autonomous Systems

Edge wins in the wild

Touchless UV sanitation

3X

more completed cycles, 60% fewer abandoned cycles, less than 1s trigger-to-start latency, and 100% cycle logging for compliance.

Vision-guided assembly/QC

17%

efficiency improvement and a 6.4× ROI forecast after line trials, driven by earlier defect capture and guided operator workflows.

Generator operations

25%

reduction in unplanned downtime and 30% fewer site visits through remote diagnostics and controlled field updates.

Networked smoke detection

20%

fewer false alarms, 40% less inspection prep time, and 25% lower MTTR through centralized system status and guided troubleshooting

Got questions?

Find your answers here.

Do you write low-level drivers and bootloaders?

Yes—bring-up, drivers, and bootloaders with clean HALs and versioning.

Do you handle production hardware?

We handle prototype and pilot; for production runs we collaborate with your OEM/EMS and hand over specs/tests.

Can you integrate with our cloud?

Yes—minimal secure ingest, registry, schemas, and alert hooks that plug into your stack.

Who owns the IP?

You own custom code and artifacts; our reusable accelerators remain ours.

Can you work alongside internal and vendor teams?

Absolutely—shared benches, interface reviews, and clear ownership maps.

What do you need from us to start?

Target envelopes (latency/accuracy/power), sample hardware/signals, environment constraints, and a security POC.